## Microcontroller power management

#### PLC18V8Z APPLICATIONS

The 80C51 microcontroller and its CMOS derivatives have two power reducing modes, Idle and Power Down. The Power Down mode reduces the device's current to less than  $50\mu A$  by only keeping the on-chip RAM and SFRs data intact. In order to resume operation while in the Power Down mode, it is necessary to apply a reset to the microcontroller.

The PLC18V8Z is in a low power mode whenever its inputs are not switching, drawing less than 100 $\mu$ A. An input transition causes the PLC18V8Z to power up its internal array for a short time, latch a valid output and then return to low power mode. Because of this transparent power reduction feature and its programmability, the PLC18V8Z is an excellent device to use in low power applications with an 80C51 microcontroller.

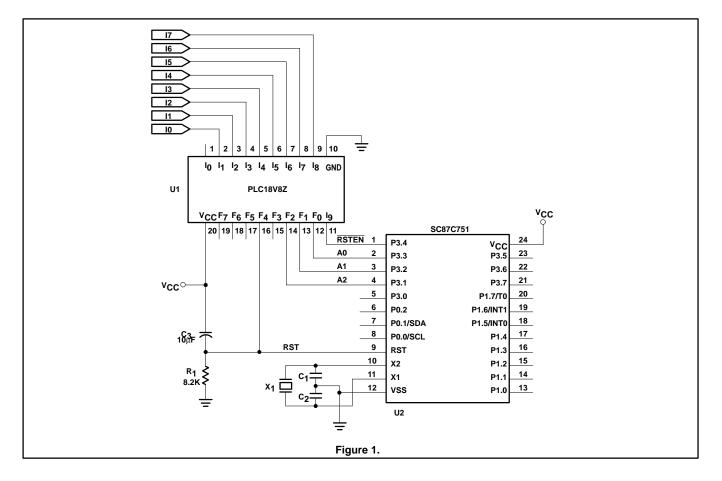

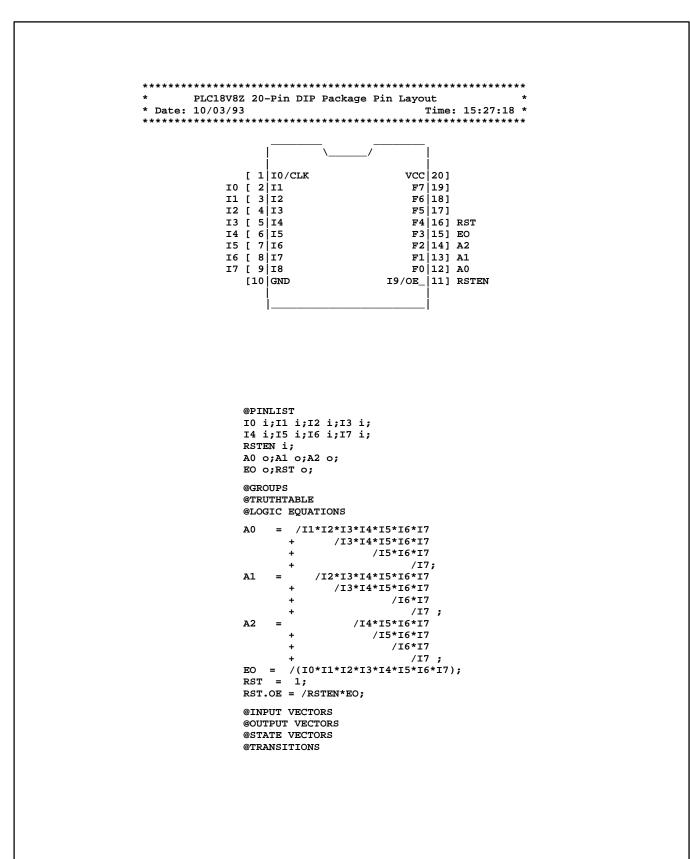

Two examples of using the PLC18V8Z with a SC87C751 microcontroller are presented. Both applications use the PLC18V8Z to detect events while the SC87C751 is in a Power Down mode and then reset (wake up) the microcontroller. The first example, shown in Figure 1, uses the PLC18V8Z as an 8-bit priority encoder. SNAP pin layout and listing of the circuitry fused inside the PLC18V8Z is shown in Figure 2.

Whenever one of the inputs  $I_7 - I_0$  goes LOW, a binary representation of its position is output on pins  $A_3 - A_0$ . If more than one input is Active-LOW, then the input with the highest priority is represented on the output, where  $I_7$ has the highest priority. Another output, EO, is not connected to the microcontroller but is used to control the RST output of the PLC18V8Z. EO is Active-LOW anytime all inputs are high. Actually, the PLC18V8Z could easily be reprogrammed to output the inverse of this signal which could be tied to the interrupt line of the microcontroller to generate an interrupt anytime one or more inputs were low.

Pin 16 of the PLC18V8Z, labeled RST, is the output of a 3-State buffer whose input is always high. The buffer's control line is tied internally to a product term which is enabled by EO and an input from the microcontroller labeled RSTEN. The RST buffer may be in only two states, either driving a high (resetting the SC87C751) or 3-State (allowing  $C_3$  to discharge), enabling normal operation

of the microcontroller. Before entering the Power Down mode, the microcontroller should force  $\overrightarrow{RSTEN}$  low. Then, any low on I<sub>7</sub> – I<sub>0</sub> will cause  $\overrightarrow{EO}$  and also RST high, resetting the microcontroller. When the microcontroller is reset, it will force its ports to input mode and since P<sub>1</sub> and P<sub>3</sub> have internal pull-up resistors,  $\overrightarrow{RSTEN}$  will go high forcing RST into the 3-State mode allowing C<sub>3</sub> to discharge.

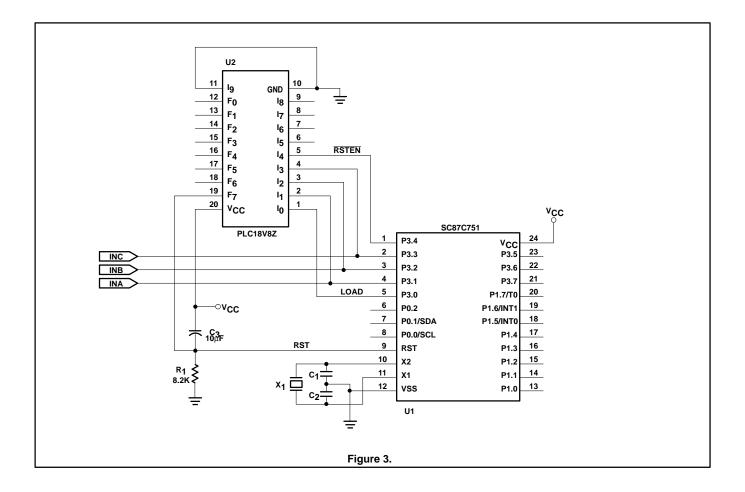

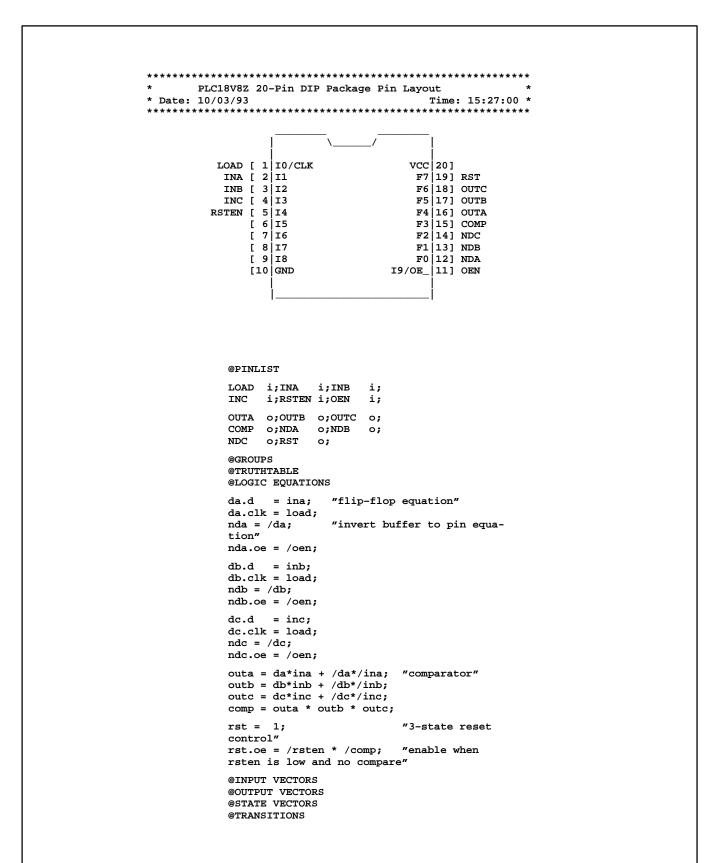

The second example, shown in Figure 3, with SNAP pin layout and listing in Figure 4, uses the PLC18V8Z to monitor three microcontroller input lines (I<sub>NC</sub> - I<sub>NA</sub>) and reset the microcontroller upon any change. Three internal registers inside the PLC18V8Z are used to hold the states or levels of the input lines prior to entering Power Down mode. Before entering Power Down mode, the microcontroller should clock into the PLC18V8Z the states of  $I_{NC} - I_{NA}$  with the LOAD signal. Comparator logic fused into the PLC18V8Z compares the output of the registers to the three input lines. The RST output of the PLC18V8Z operates in a similar manner to the first example to reset the microcontroller whenever RSTEN is low and the output of the comparator is false.

#### AN0302

# Microcontroller power management

# Application Note

# Microcontroller power management

## AN0302

# Microcontroller power management

Figure 4.

AN0302

Application Note